With their high performance functionality and high extensibility, PF SoC reduces risks

associated with the development of SoCs and achieves low power consumption of products.

High Performance CPUs

PF SoCs have multiple ARM Cortex-A15* CPU cores that allow them to operate at high speeds. In addition

to the Cortex-A15, PF SoCs also have ARM Cortex-A7 CPU cores, which are compatible with the Cortex-A15 as well as

the software used and have low power consumption. By using these CPU cores and configuring the big.LITTLE

architecture proposed by ARM, PF SoCs meet two conflicting needs—high processing performance and low-power

operation—at a high level. These CPU cores can also be used independently as AMP (asymmetric multiprocessing)

processors. *Excluding the MB86S73

Advanced GPUs

In addition to their high performance CPUs, PF SoCs have ARM Mali-T624 GPUs. Using the advanced

Mali-T624 GPU, PF SoCs achieve GPGPU computing that improves the performance of overall parallel computing as well

as sophisticated graphics processing.

High Extensibility

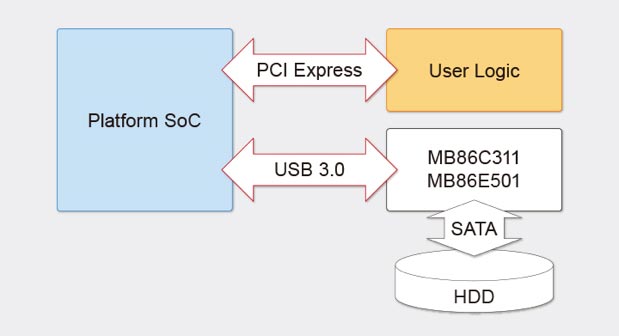

Function Enhancement with PCI Express

The PF SoC has PCI Express. By connecting user logic and the PF SoC, users can use both the logic that is their unique advantage and a CPU with high processing performance.

The PF SoC has PCI Express. By connecting user logic and the PF SoC, users can use both the logic that is their unique advantage and a CPU with high processing performance.

Function Enhancement with USB

As an example of function enhancement with USB, a SATA interface can be enhanced by connecting Socionext's USB3.0-SATA bridge LSI (MB86C311/MB86E501) to a PF SoC to enable hard disks (HDD) and other storage devices to be connected to it.

As an example of function enhancement with USB, a SATA interface can be enhanced by connecting Socionext's USB3.0-SATA bridge LSI (MB86C311/MB86E501) to a PF SoC to enable hard disks (HDD) and other storage devices to be connected to it.

Low Power Consumption

Standby and Response Function

PF SoCs have a standby and response function for enabling power saving on devices with network interfaces. By stopping the supply of power to network devices when they are in an idle state and autonomously responding to access from the network as a proxy, this function reduces the power consumption of the system while maintaining a connection with the network. In the event that the system receives data requiring a system restart, the function turns on the power to the CPU to enable the system to start quickly.

PF SoCs have a standby and response function for enabling power saving on devices with network interfaces. By stopping the supply of power to network devices when they are in an idle state and autonomously responding to access from the network as a proxy, this function reduces the power consumption of the system while maintaining a connection with the network. In the event that the system receives data requiring a system restart, the function turns on the power to the CPU to enable the system to start quickly.

DDR Retention Mode

PF SoCs have a function to set memory devices to self-refresh mode, in which the power of the PF SoC, excluding the minimum required blocks, is shut down (DDR retention mode). This innovative feature allows PF SoCs to stand by with low power consumption that is well below 1 mW and to quickly start up when resuming from standby. This feature contributes to the reduction of system power consumption and resumption time when a system is operated using a battery for the power supply.

PF SoCs have a function to set memory devices to self-refresh mode, in which the power of the PF SoC, excluding the minimum required blocks, is shut down (DDR retention mode). This innovative feature allows PF SoCs to stand by with low power consumption that is well below 1 mW and to quickly start up when resuming from standby. This feature contributes to the reduction of system power consumption and resumption time when a system is operated using a battery for the power supply.

Fine Power Domain Control

By stopping the power supply to functions of the SoC that are not in use, system power consumption can be reduced. PF SoCs divide the entire SoC into multiple power domains in order to enable fine power control.

By stopping the power supply to functions of the SoC that are not in use, system power consumption can be reduced. PF SoCs divide the entire SoC into multiple power domains in order to enable fine power control.

Reduced Risk in Custom SoC Development

Reduced Risk in Custom SoC Development

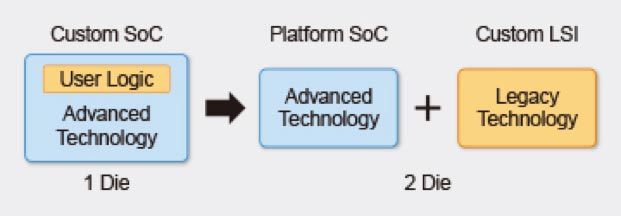

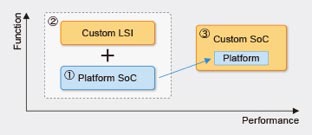

There are largely two types of approaches for realizing user-specific functions with LSI and configuring the system: an approach of developing a totally new SoC with user logic (③) and another approach of developing new LSI with user logic only for the difference with the PF SoC and using them as a chipset (②).

There are largely two types of approaches for realizing user-specific functions with LSI and configuring the system: an approach of developing a totally new SoC with user logic (③) and another approach of developing new LSI with user logic only for the difference with the PF SoC and using them as a chipset (②).

Even when developing a new custom SoC (③), various risks can be

reduced by developing it based on the existing PF SoC (①). The components of the PF SoC, including CPU/GPU cores,

memory interface block associated with them, media processing block, and high-speed interface block, have been

defined previously. Reusing for them when developing a new SoC allows you to significantly reduce the time required

for logical design and verification. You can start developing software without waiting for the completion of the

engineering sample (ES).

Meanwhile, using a chipset (②) has the following advantages. As the development costs will be reduced and the development period will be shorter in such development, it is possible to start evaluating a custom LSI using a board with an ES within three months, at the earliest, from the start of development of the custom LSI.

Meanwhile, using a chipset (②) has the following advantages. As the development costs will be reduced and the development period will be shorter in such development, it is possible to start evaluating a custom LSI using a board with an ES within three months, at the earliest, from the start of development of the custom LSI.