DDR接口

从低中速传输带宽到高速传输带宽和Low Power,我公司提供各种工艺的多样的DDR接口、宏。 另外通过使用LSI–Package–Board协调设计的设计支援,我们支持定制化Soc开发。

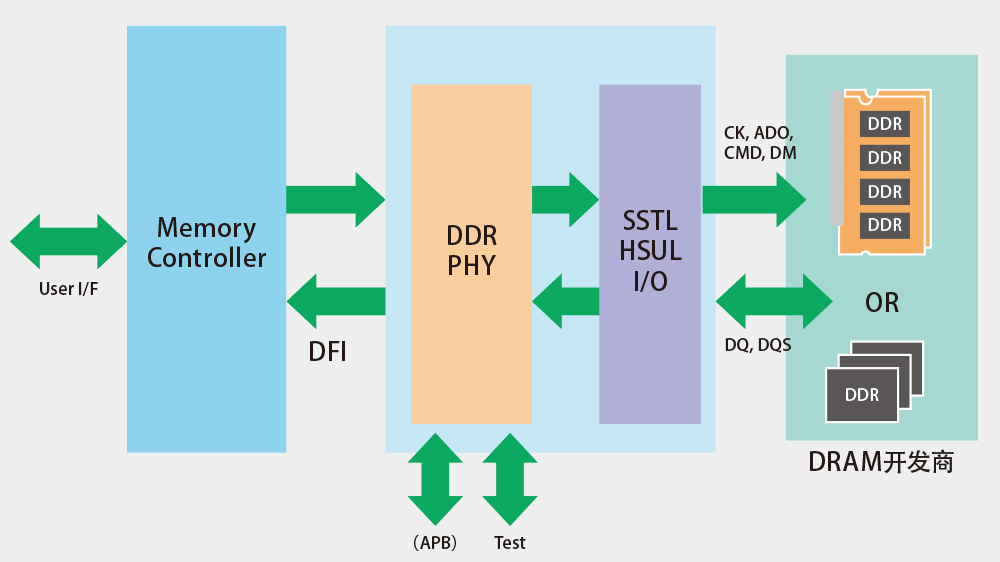

[DDR接口、宏]

高速/高带宽(高速宏):DDR3/DDR4

Low Power(低功耗宏):LPDDR4/LPDDR3/LPDDR2/DDR3L

遵守DFI (所有宏)

通过PHY (Training功能) ,支持Fly-by、PoP、etc. 多样的DRAM配置、PKG选项

Low Power(低功耗宏):LPDDR4/LPDDR3/LPDDR2/DDR3L

遵守DFI (所有宏)

通过PHY (Training功能) ,支持Fly-by、PoP、etc. 多样的DRAM配置、PKG选项

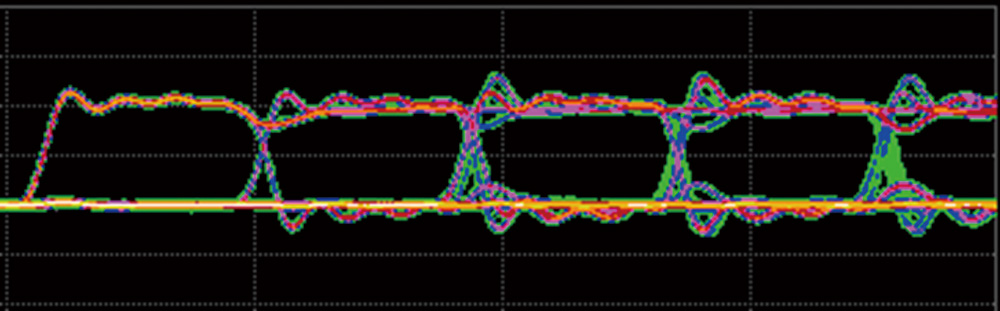

[支持DDR接口设计(LSI–Package–Board 协调设计)]

Timing验证:验证包括 LSI.I/O ~ DRAM间延迟的DDR- IF整个系列的Timing

Power Integrity:作为 电源 Impedance设计优化寄存电感、共振频率、电源(PKG,PCB)阻抗

Signal Integrity:Driver Strength、终端电阻、布线Topology的优化

Power Integrity:作为 电源 Impedance设计优化寄存电感、共振频率、电源(PKG,PCB)阻抗

Signal Integrity:Driver Strength、终端电阻、布线Topology的优化

[DDR接口结构图]

[LPDDR4-2400 DQ波形]

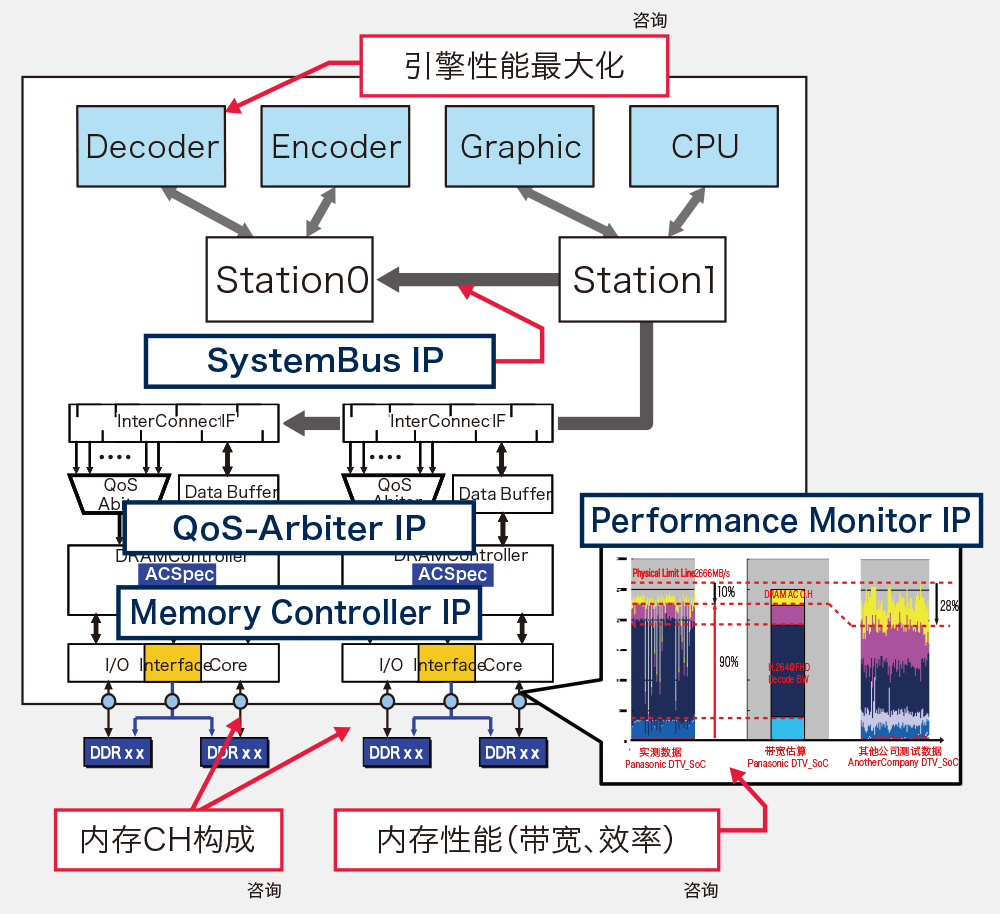

内存控制器

我们为优化系统提供各种内存的解决方案。另外在内存通道、系统总线方面,进行内存系统的咨询来提升客户的SoC性能。

内存控制器IP

提高DRAM使用率的控制器

QoS-判优器IP

高性能、高功能的多功能QoS -判优器

BusIP

低功耗布局灵活性高的独创总线

MonitorIP

实时显示内存系统性能

监控性能(带宽、Latency),提供调谐参数环境。

监控性能(带宽、Latency),提供调谐参数环境。

SLVS-EC接口

搭建与高速、高解析度CMOS 图像传感器连接的摄像系统的高速接口。

提供具备最大18.4 Gbps的高带宽,实现高映像表现力的解决方案。

提供具备最大18.4 Gbps的高带宽,实现高映像表现力的解决方案。

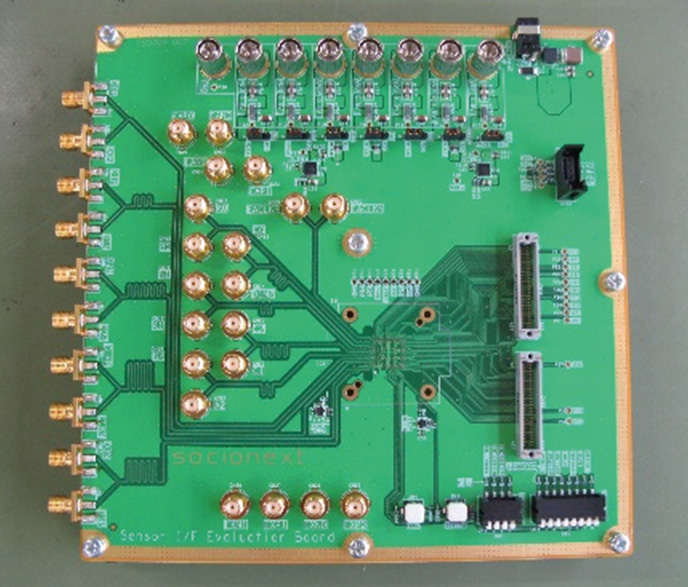

SLVS-EC评估板

SLVS-EC宏

支持最大通道数 x8

带有错误检测、修改功能(Reed-Solomon ECC)

可选择Multiple Stream传输

带有错误检测、修改功能(Reed-Solomon ECC)

可选择Multiple Stream传输

10G–28Gbps SerDes接口

每个通道具备10 Gbps~28 Gbps的传输性能,通过组成多个通道,我公司可以提供用于构建100 G/200 G/400 G的Optical network和100 G Ether系统的高性能SERDES宏。 通过内置低抖动的高性能PLL,可实现每个通道最大28 Gbps的强大的传输功能。支持OIF-CEI-11G-SR, OIF-CEI-28G-SR, OIF-CEI-28GVSR,IEEE802.3ba CAUI, IEEE802.3bm CAUI4, XFI等各种规格。

特点

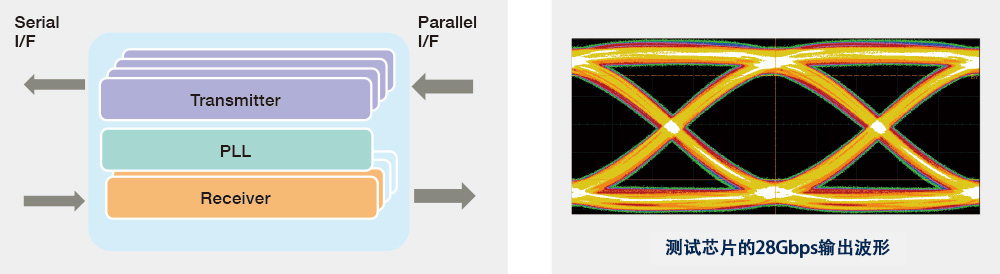

• x1, x4LANE构成• 由Transmitter/Receier/PLL组成,一个宏可进行双向通信

• 每个宏最大112.8 Gbps(单向,x4构成时)

• 支持每个LANE的断电控制

• 支持宏整体断电控制

• 带有各个Receiver lane的Clock-Data recovery

• 支持Transmitter Equalization

• 支持Receiver Equalization

• 在Transmitter/Receiver内置终端电阻

• 有机倒装芯片封装(0.8 mm/1.0 mm Ball Pitch, HDBU Package)