Front-end Design kit

We offer a development environment using standard EDA tools as a SoC development environment for customers and a tool we created for improving design efficiency as a design kit. The front-end design kit, which is uniquely optimized by Socionext, enables the development of high performance, small chip size, low power LSIs.

[Socionext Front-end Design kit]

| High level synthesis | Catapult*3, C-to-Silicon Compiler*1, Stratus*1 | |

|---|---|---|

| RTL style check | SpyGlass*2 | |

| Functional verification | Verilog-HDL | Incisive Enterprise Simulator*1, Questa*3, VCS-MX,VCS*2 |

| VHDL | Incisive Enterprise Simulator*1, Questa*3, VCS-MX*2 | |

| CPF/UPF | Incisive Enterprise Simulator-XL*1, Questa*3, VCS-NLP*2 | |

| Logic synthesis | Design Compiler*2, Encounter RTL Compiler*1, Genus Synthesis Solution*1 | |

| Equivalence verification | Encounter Conformal Equivalence Checker*1, Formality*2 | |

| Timing constraint verification | Encounter Conformal Constraint Designer*1, SpyGlass Constraints*2 | |

| MV verification | Encounter Conformal Lowpower*1, VC Static Low Power*2 | |

| Analysis/debugger | Verdi*2 | |

| Netlist check*4 | SpyGlass*2 | |

| Pre-DFT check*4 | SpyGlass DFT*2 | |

*1:Cadence, Inc.

*2:Synopsys, Inc.

*3:Mentor Graphics Co.

*4:We provide a checker we developed in-house to suit the technology.

*2:Synopsys, Inc.

*3:Mentor Graphics Co.

*4:We provide a checker we developed in-house to suit the technology.

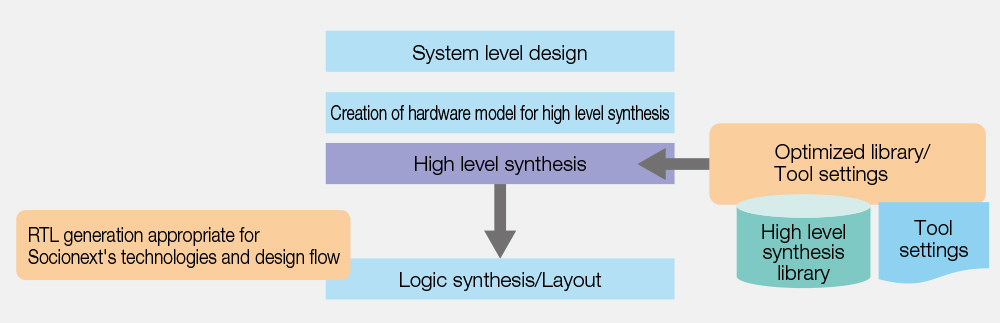

High level Synthesis

As chips becomes larger in scale and more complicated, the design environment customers use is also advancing from conventional RTL design to system level design and verification using higher abstraction languages (C++/SystemC). Under these circumstances, it has become common to perform high level synthesis from a high abstraction model to RTL for shorter TAT in RTL design. Socionext provides technology libraries optimized for each high level synthesis tool and documentation describing optimization settings to generate appropriate RTL for our technology and design flow in such high level synthesis.