前端设计套件

作为客户的SoC开发环境,本公司将借助标准EDA工具的开发环境和设计高效化的本公司开发工具,以设计套件方式提供给客户,并提供相应的支持。该前端设计套件是本公司独创优化的,可在短时间内实现高性能、小尺寸、低功率的LSI的开发。

[前端设计套件支持EDA工具]

| 高位综合 | Catapult*3, C-to-Silicon Compiler*1, Stratus*1 | |

|---|---|---|

| RTL 样式检验 | SpyGlass*2 | |

| 功能验证 | Verilog-HDL | Incisive Enterprise Simulator*1, Questa*3, VCS-MX,VCS*2 |

| VHDL | Incisive Enterprise Simulator*1, Questa*3, VCS-MX*2 | |

| CPF/UPF | Incisive Enterprise Simulator-XL*1, Questa*3, VCS-NLP*2 | |

| 逻辑综合 | Design Compiler*2, Encounter RTL Compiler*1, Genus Synthesis Solution*1 | |

| 等价验证 | Encounter Conformal Equivalence Checker*1, Formality*2 | |

| 时序制约验证 | Encounter Conformal Constraint Designer*1, SpyGlass Constraints*2 | |

| MV 验证 | Encounter Conformal Lowpower*1, VC Static Low Power*2 | |

| 解析・调试器 | Verdi*2 | |

| Netlist检验*4 | SpyGlass*2 | |

| Pre DFT检验*4 | SpyGlass DFT*2 | |

*1:日本Cadence Design Systems公司

*2:日本Synopsys合同会社

*3:Mentor Graphics Japan株式会社

*4:依据不同工艺提供自制的检验工具

*2:日本Synopsys合同会社

*3:Mentor Graphics Japan株式会社

*4:依据不同工艺提供自制的检验工具

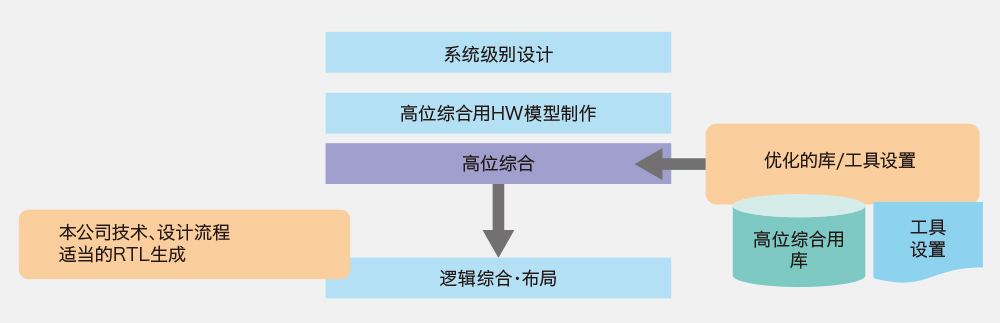

高位综合

随着芯片的大规模化和复杂化,客户设计环境也从原有的RTL设计、进化到使用更高抽象度的高级语言(C++/SystemC)的系统级设计和验证。在这种情况下,由于RTL设计的短TAT的需求,从高抽象度模型向RTL进行高位综合已经很普遍。本公司为了针对本公司技术和设计流程生成适合的RTL,以高综合方式提供为各高位综合工具进行优化的技术库和最佳设定的资料和文档。